Die Elektronikindustrie nähert sich einer Grenze für die Anzahl der Transistoren, die auf der Oberfläche eines Computerchips untergebracht werden können. Die Chiphersteller wollen additionally eher aufbauen als verschwinden.

Anstatt immer kleinere Transistoren auf eine einzige Oberfläche zu quetschen, strebt die Industrie danach, mehrere Oberflächen aus Transistoren und Halbleiterelementen zu stapeln – vergleichbar mit der Umwandlung eines Ranchhauses in ein Hochhaus. Solche mehrschichtigen Chips könnten exponentiell mehr Daten verarbeiten und viel komplexere Funktionen ausführen als die heutige Elektronik.

Eine erhebliche Hürde ist jedoch die Plattform, auf der die Chips aufgebaut sind. Heutzutage dienen sperrige Siliziumwafer als Hauptgerüst, auf dem hochwertige, einkristalline Halbleiterelemente wachsen. Jeder stapelbare Chip müsste als Teil jeder Schicht einen dicken Silizium-„Boden“ enthalten, der die Kommunikation zwischen funktionalen Halbleiterschichten verlangsamt.

Jetzt haben MIT-Ingenieure einen Weg gefunden, diese Hürde zu umgehen, und zwar mit einem mehrschichtigen Chip-Design, das keine Silizium-Wafer-Substrate erfordert und bei Temperaturen arbeitet, die niedrig genug sind, um die Schaltkreise der darunter liegenden Schicht zu erhalten.

In einer Studie erscheint heute in der Zeitschrift Naturberichtet das Group mit der neuen Methode zur Herstellung eines mehrschichtigen Chips mit abwechselnden Schichten aus hochwertigem Halbleitermaterial, die direkt übereinander gewachsen sind.

Die Methode ermöglicht es Ingenieuren, Hochleistungstransistoren sowie Speicher- und Logikelemente auf jeder beliebigen kristallinen Oberfläche zu bauen – nicht nur auf dem sperrigen Kristallgerüst von Siliziumwafern. Ohne diese dicken Siliziumsubstrate könnten mehrere Halbleiterschichten in direkterem Kontakt stehen, was zu einer besseren und schnelleren Kommunikation und Berechnung zwischen den Schichten führt, sagen die Forscher.

Die Forscher stellen sich vor, dass mit der Methode KI-{Hardware} in Type von gestapelten Chips für Laptops oder tragbare Geräte gebaut werden könnte, die so schnell und leistungsstark wäre wie heutige Supercomputer und riesige Datenmengen auf Augenhöhe mit physischen Rechenzentren speichern könnte.

„Dieser Durchbruch eröffnet der Halbleiterindustrie ein enormes Potenzial und ermöglicht das Stapeln von Chips ohne herkömmliche Einschränkungen“, sagt Studienautor Jeehwan Kim, außerordentlicher Professor für Maschinenbau am MIT. „Dies könnte zu einer Verbesserung der Rechenleistung für Anwendungen in den Bereichen KI, Logik und Speicher um Größenordnungen führen.“

Zu den MIT-Co-Autoren der Studie gehören der Erstautor Ki Seok Kim, Seunghwan Search engine optimisation, Doyoon Lee, Jung-El Ryu, Jekyung Kim, Jun Min Suh, June-chul Shin, Min-Kyu Music, Jin Feng und Sangho Lee Mitarbeiter des Samsung Superior Institute of Expertise, der Sungkyunkwan College in Südkorea und der College of Texas in Dallas.

Samentaschen

Im Jahr 2023 wird Kims Gruppe gemeldet dass sie eine Methode entwickelten, um hochwertige Halbleitermaterialien auf amorphen Oberflächen wachsen zu lassen, ähnlich der vielfältigen Topographie halbleitender Schaltkreise auf fertigen Chips. Das Materials, das sie züchteten, battle eine Artwork 2D-Materials, bekannt als Übergangsmetalldichalkogenide (TMDs), das als vielversprechender Nachfolger von Silizium für die Herstellung kleinerer Hochleistungstransistoren gilt. Solche 2D-Materialien können ihre halbleitenden Eigenschaften auch auf der Skala eines einzelnen Atoms beibehalten, während die Leistung von Silizium stark abnimmt.

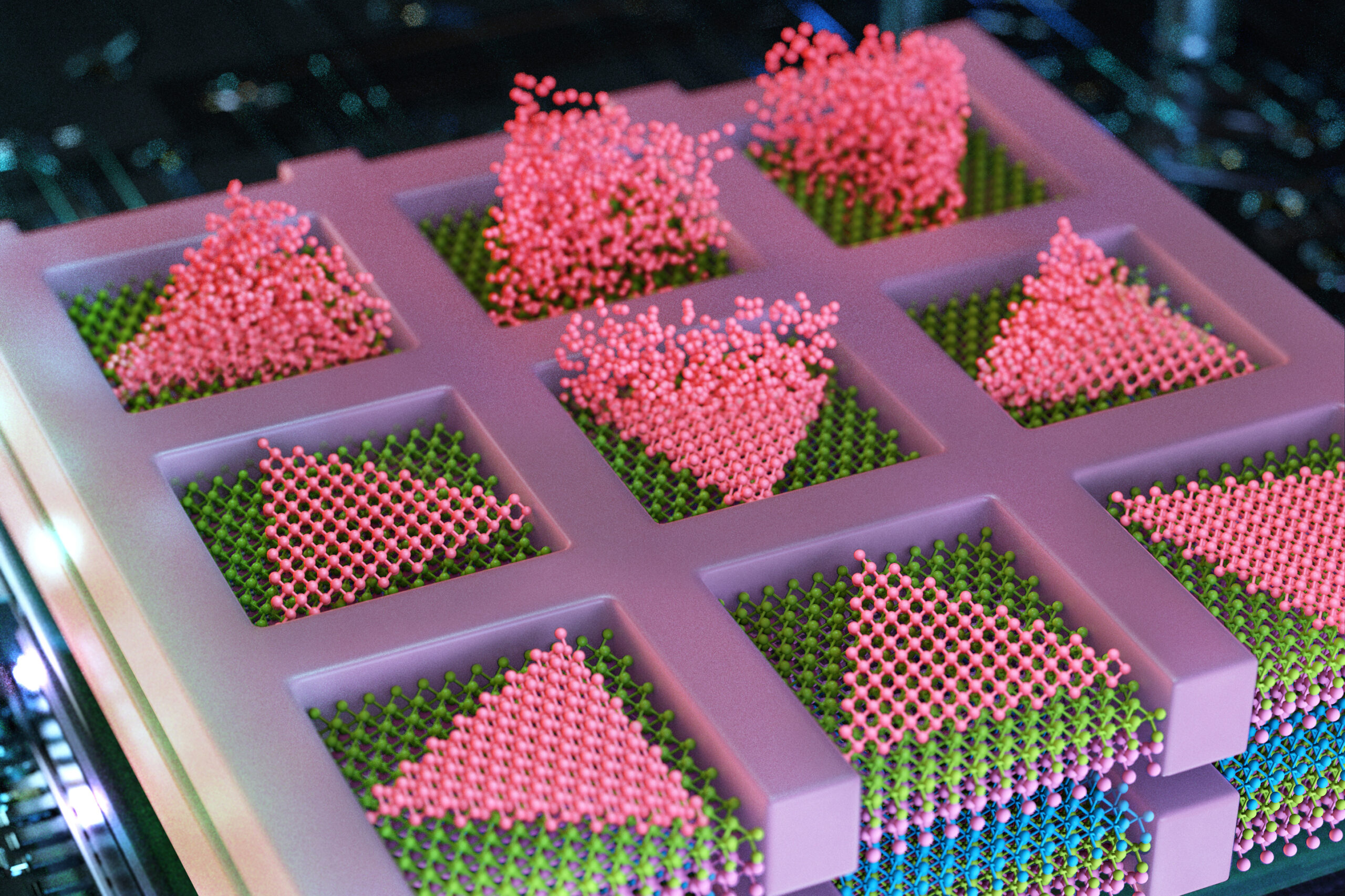

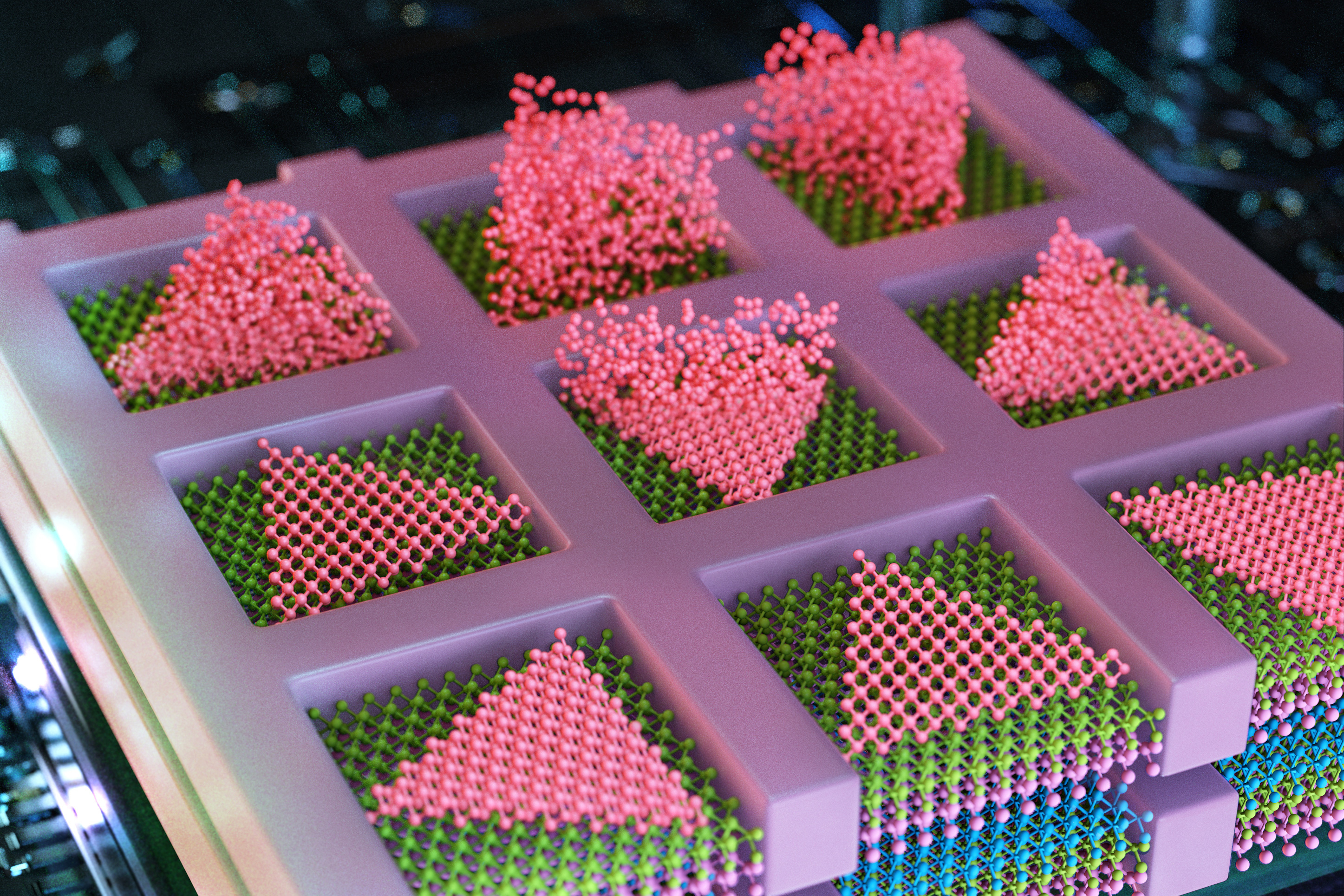

In ihrer vorherigen Arbeit züchtete das Group TMDs auf Siliziumwafern mit amorphen Beschichtungen sowie auf bestehenden TMDs. Um Atome dazu zu ermutigen, sich in hochwertiger einkristalliner Type statt in zufälliger, polykristalliner Unordnung anzuordnen, bedeckten Kim und seine Kollegen zunächst einen Siliziumwafer mit einem sehr dünnen Movie oder einer „Maske“ aus Siliziumdioxid, die sie strukturierten winzige Öffnungen oder Taschen. Dann ließen sie ein Fuel aus Atomen über die Maske strömen und stellten fest, dass sich Atome als „Samen“ in den Taschen festsetzten. Die Taschen beschränkten die Samen darauf, in regelmäßigen, einkristallinen Mustern zu wachsen.

Allerdings funktionierte die Methode damals nur bei etwa 900 Grad Celsius.

„Man muss dieses einkristalline Materials bei unter 400 Grad Celsius wachsen lassen, sonst ist der darunter liegende Schaltkreis völlig verkocht und zerstört“, sagt Kim. „Unsere Hausaufgabe bestand additionally darin, eine ähnliche Technik bei Temperaturen unter 400 Grad Celsius durchzuführen. Wenn wir das schaffen könnten, wären die Auswirkungen erheblich.“

Aufbauend

In ihrer neuen Arbeit wollten Kim und seine Kollegen ihre Methode verfeinern, um einkristalline 2D-Materialien bei Temperaturen zu züchten, die niedrig genug sind, um alle darunter liegenden Schaltkreise zu erhalten. Sie fanden eine überraschend einfache Lösung in der Metallurgie – der Wissenschaft und dem Handwerk der Metallproduktion. Wenn Metallurgen geschmolzenes Metall in eine Type gießen, bildet die Flüssigkeit langsam „Keime“ oder bildet Körner, die wachsen und zu einem regelmäßig gemusterten Kristall verschmelzen, der zu einer festen Type aushärtet. Metallurgen haben herausgefunden, dass diese Keimbildung am leichtesten an den Rändern einer Type auftritt, in die flüssiges Metall gegossen wird.

„Es ist bekannt, dass die Keimbildung an den Rändern weniger Energie – und Wärme – erfordert“, sagt Kim. „Additionally haben wir dieses Konzept aus der Metallurgie übernommen, um es für zukünftige KI-{Hardware} zu nutzen.“

Das Group wollte einkristalline TMDs auf einem Siliziumwafer züchten, der bereits mit Transistorschaltkreisen hergestellt wurde. Wie bei ihren vorherigen Arbeiten bedeckten sie zunächst die Schaltkreise mit einer Maske aus Siliziumdioxid. Anschließend lagerten sie TMD-„Samen“ an den Rändern jeder Maskentasche ab und stellten fest, dass diese Randkeime bei Temperaturen von bis zu 380 Grad Celsius zu einkristallinem Materials heranwuchsen, im Vergleich zu Samen, die in der Mitte, weiter weg, zu wachsen begannen die Ränder jeder Tasche, was höhere Temperaturen erforderte, um einkristallines Materials zu bilden.

Die Forscher gingen noch einen Schritt weiter und nutzten die neue Methode, um einen mehrschichtigen Chip mit abwechselnden Schichten aus zwei verschiedenen TMDs herzustellen – Molybdändisulfid, ein vielversprechender Materialkandidat für die Herstellung von n-Typ-Transistoren; und Wolframdiselenid, ein Materials, das das Potenzial hat, in p-Typ-Transistoren verarbeitet zu werden. Sowohl p- als auch n-Typ-Transistoren sind die elektronischen Bausteine zur Ausführung jeder logischen Operation. Dem Group gelang es, beide Materialien in einkristalliner Type direkt übereinander wachsen zu lassen, ohne dass zwischengeschaltete Siliziumwafer erforderlich waren. Kim sagt, dass die Methode die Dichte der Halbleiterelemente eines Chips effektiv verdoppeln wird, insbesondere des Metalloxid-Halbleiters (CMOS), der ein Grundbaustein moderner Logikschaltungen ist.

„Ein mit unserer Technik realisiertes Produkt ist nicht nur ein 3D-Logikchip, sondern auch 3D-Speicher und deren Kombinationen“, sagt Kim. „Mit unserer wachstumsbasierten monolithischen 3D-Methode könnten Sie Dutzende bis Hunderte von Logik- und Speicherschichten direkt übereinander wachsen lassen, und sie wären in der Lage, sehr intestine zu kommunizieren.“

„Herkömmliche 3D-Chips wurden mit dazwischen liegenden Siliziumwafern hergestellt, indem Löcher durch die Wafer gebohrt wurden – ein Prozess, der die Anzahl der gestapelten Schichten, die vertikale Ausrichtungsauflösung und die Ausbeute begrenzt“, fügt Erstautor Kiseok Kim hinzu. „Unsere wachstumsbasierte Methode befasst sich mit all diesen Problemen auf einmal.“

Um ihr stapelbares Chipdesign weiter zu kommerzialisieren, hat Kim kürzlich ein Unternehmen namens FS2 (Future Semiconductor 2D Supplies) ausgegliedert.

„Wir zeigen bisher ein Konzept für kleine Gerätearrays“, sagt er. „Der nächste Schritt ist die Skalierung, um den Betrieb eines professionellen KI-Chips zu zeigen.“

Diese Forschung wird teilweise vom Samsung Superior Institute of Expertise und dem US Air Drive Workplace of Scientific Analysis unterstützt.